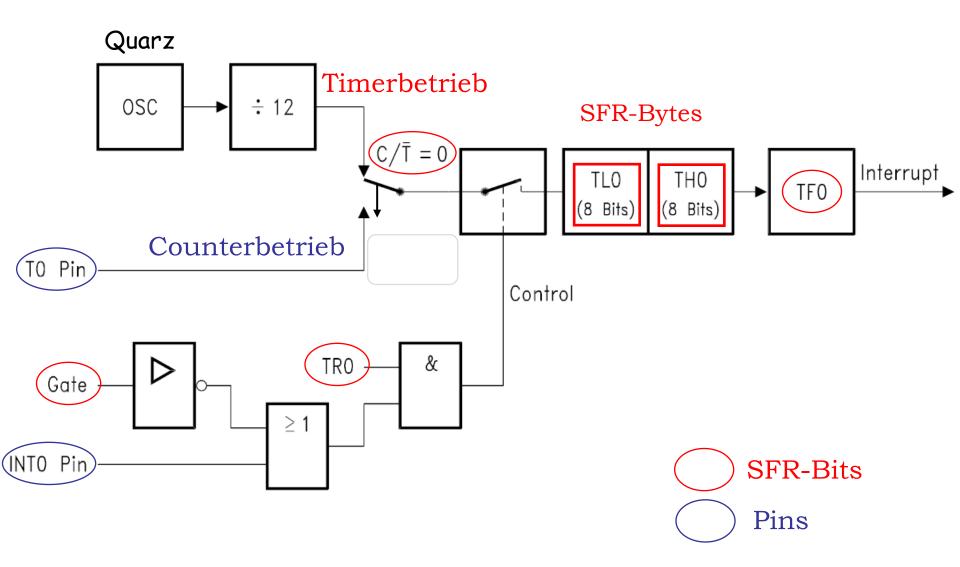

#### Blockschaltbild zur Funktion von Timer 'T0' in der Betriebsart 1

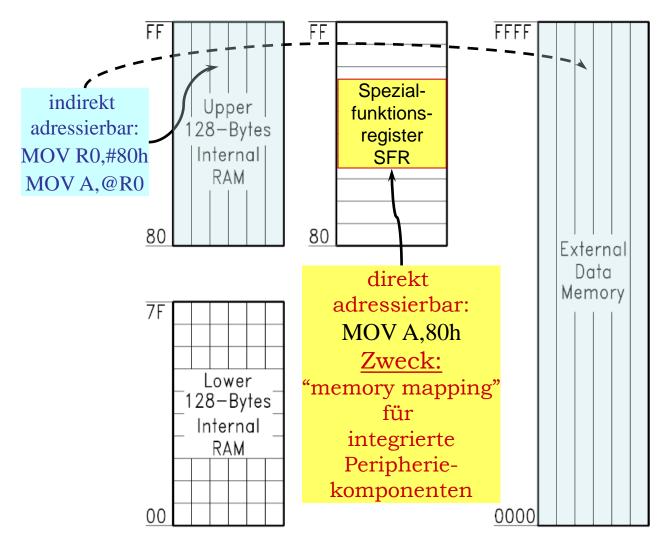

### Typische Speicherstruktur konventioneller Mikrocontroller

Data Memory

| ISPI               | WC   | ΟI | SPE          | SP   | IM | CPOL          | CPHA  | SPR1       | SPR0          |      | \      | SPICON1              | DAC0L    | DAC0H    | DAC1L    | DAC1H                 | DACCON    |           |                    |

|--------------------|------|----|--------------|------|----|---------------|-------|------------|---------------|------|--------|----------------------|----------|----------|----------|-----------------------|-----------|-----------|--------------------|

|                    |      |    |              |      |    | FBH 0         | l     |            | F8H 0         | BITS | >      | F8H 04H              | F9H 00H  | FAH 00H  | FBH 00H  | FCH 00H               | FDH 04H   | RESERVED  | RESERVED           |

|                    | 1    |    |              | 1    |    |               |       | _          | 1             | 1    | (      | B <sup>1</sup>       | _        | _        | _        | ADCGAINH <sup>3</sup> |           |           | SPIDAT             |

| F7H 0              | F6H  | 0  | F5H 0        | F4H  | 0  | F3H 0         | F2H   | F1H (      | FOH 0         | BITS | >      | FOH OOH              | F1H 00H  | F2H 20H  | F3H 00H  | F4H 00H               | F5H 00H   | RESERVED  | F7H 00H            |

|                    |      |    |              |      |    |               |       |            | 1             | 1    | (      | _                    | FIR OUR  | F2H 20H  | F3H 00H  | F#H 00H               | FOR OUR   |           | ADCCON1            |

| I2CSI/MDO<br>EFH 0 |      |    | EDH 0        |      |    |               | I2CRS |            | I2CI<br>E8H 0 | BITS | >      | I2CCON <sup>1</sup>  | RESERVED | RESERVED | RESERVED | RESERVED              | RESERVED  | RESERVED  |                    |

| LIII 0             |      |    | LDII 0       | LOII |    | LBII 0        | LAII  |            |               |      | _      | E8H 00H              |          |          |          |                       |           |           | EFH 40H            |

| F711 0             | Foll | _  | E 511 0      |      | •  | F211 0        | F011  |            |               | BITS | >      | ACC1                 | RESERVED | RESERVED | RESERVED | RESERVED              | RESERVED  | RESERVED  | RESERVED           |

| E7H 0              | E6H  | 0  | E5H 0        | E4H  | U  | E3H 0         | E2H   | D E1H (    | ) E0H 0       |      |        | E0H 00H              |          |          |          |                       |           |           |                    |

| ADCI               | DN   |    | CCON         |      |    |               | CS2   | CS1        | CS0           | BITS | \      | ADCCON2 <sup>1</sup> | ADCDATAL | ADCDATAH | RESERVED | RESERVED              | RESERVED  | RESERVED  | PSMCON             |

| DFH 0              | DEH  | 0  | DDH 0        | DCH  | 0  | DBH 0         | DAH   | D9H (      | D8H 0         |      |        | D8H 00H              | D9H 00H  | DAH 00H  |          |                       |           |           | DFH DEH            |

| CY                 | A    | С  | F0           | RS   | 31 | RS0           | OV    | FI         | Р             | BITS | \      | PSW <sup>1</sup>     | RESERVED | DMAL     | DMAH     | DMAP                  | RESERVED  | RESERVED  | PLLCON             |

| D7H 0              | D6H  | 0  | D5H 0        | D4H  | 0  | D3H 0         | D2H   | D1H (      | D0H 0         | Biro |        | D0H 00H              |          | D2H 00H  | D3H 00H  | D4H 00H               |           |           | D7H 53H            |

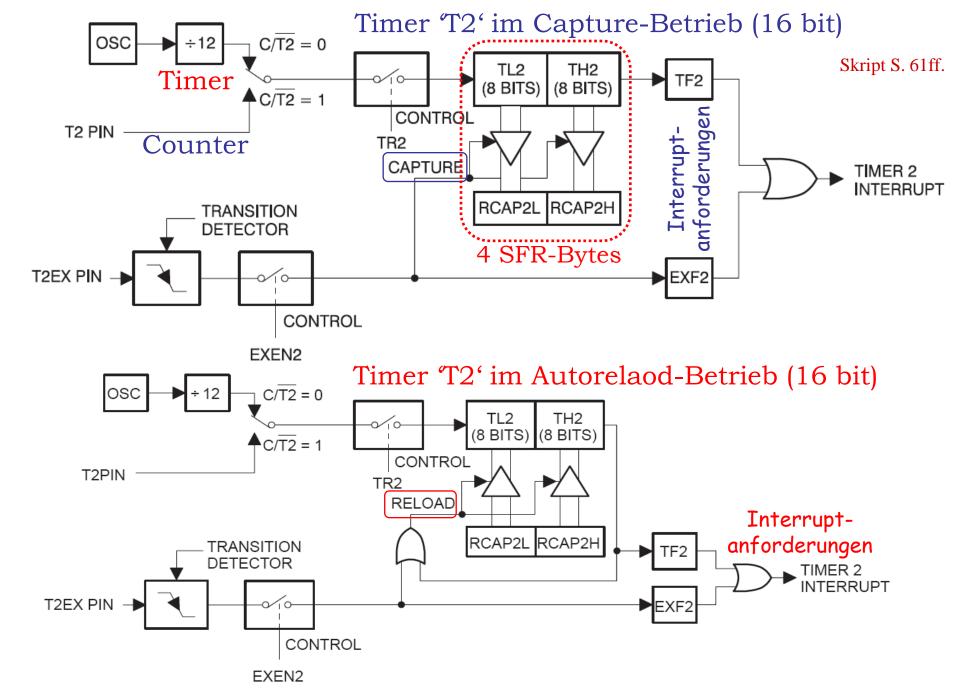

| TF2                | EX   | F2 | RCLK         | TCI  | LK | EXEN2         | TR2   | CNT2       | CAP2          | BITS | \      | T2CON1               | RESERVED | RCAP2L   | RCAP2H   | TL2                   | TH2       | RESERVED  | RESERVED           |

| CFH 0              | CEH  | 0  | CDH 0        | ССН  | 0  | CBH 0         | CAH   | СЭН (      | C8H 0         | ыз   |        | C8H 00H              | RESERVED | CAH 00H  | свн оон  | ссн оон               | CDH 00H   | RESERVED  | KESEKVED           |

| PRE3               | PR   | F2 | PRE1         | PR   | ΕO | WDIR          | WDS   | WDE        | WDWR          |      | \      | WDCON1               | RESERVED | CHIPID   | DESERVED | DE0ED\/ED             |           | EDARL     | EDARH              |

| C7H 0              |      |    | C5H 0        |      |    |               | C2H   |            | COH O         | BITS | 2      | C0H 10H              | RESERVED | C2H XXH  | RESERVED | RESERVED              | RESERVED  | C6H 00H   | C7H 00H            |

| PSI                | PAI  | nc | PT2          | PS   | 0  | PT1           | PX1   | PT0        | PX0           |      | (      | IP <sup>1</sup>      | ECON     |          |          | EDATA1                | EDATA2    | EDATA3    | EDATA4             |

| BFH 0              |      |    | BDH 0        | 1 .  | _  | BBH 0         |       | 1          |               | BITS | >      | B8H 00H              | В9Н 00Н  | RESERVED | RESERVED | BCH 00H               | BDH 00H   | BEH OOH   | BFH 00H            |

| RD                 | 10/  | _  | T4           |      | ^  | INITA         | INITO | TvD        | D.D           |      |        | P3 <sup>1</sup>      | PWM0L    | PWM0H    | PWM1L    | PWM1H                 | DDIT COIT | BEIT COIT | SPH                |

| B7H 1              | B6H  |    | T1<br>B5H 1  | T(   |    | INT1<br>B3H 1 | B2H   | TxD<br>B1H | RxD<br>B0H 1  | BITS | >      | BOH FFH              |          |          | ВЗН 00Н  | B4H 00H               | NOT USED  | NOT USED  |                    |

|                    |      |    |              |      |    |               |       |            |               |      | (      |                      |          | B2H 00H  | B3H 00H  | D411 00H              |           | DIMMAGONI | B7H 00H<br>CFG841/ |

| EA<br>AFH 0        | AEH  |    | ET2<br>ADH 0 | Y CH |    | ET1<br>ABH 0  | EX1   | ET0        | EX0           | BITS | $\geq$ | → IE¹                | IEIP2    | RESERVED | RESERVED | RESERVED              | RESERVED  | PWMCON    | CFG842             |

| AFH 0              | AER  | -  | ADH 0        | ACH  | U  | ABH 0         | AAH   | J ASH C    | ASH U         |      |        | A8H 00H              | A9H A0H  |          |          |                       |           |           | AFH 00H            |

|                    |      |    |              |      |    |               |       |            |               | BITS | >      | P2 <sup>1</sup>      | TIMECON  | HTHSEC   | SEC      | MIN                   | HOUR      | INTVAL    | DPCON              |

| A7H 1              | АбН  | 1  | A5H 1        | A4H  | 1  | A3H 1         | A2H   | I   A1H    | A0H 1         |      |        | A0H FFH              | A1H 00H  | A2H 00H  | A3H 00H  | A4H 00H               | A5H 00H   | A6H 00H   | A7H 00H            |

| SM0                | SN   |    | SM2          | RE   |    | TB8           | RB8   | TI         | RI            | BITS | \      | SCON1                | SBUF     | 12CDAT   | I2CADD   | NOT USED              | T3FD      | T3CON     | NOT USED           |

| 9FH 0              | 9EH  | 0  | 9DH 0        | 9CH  | 0  | 9BH 0         | 9AH   | 0 99H (    | 98H 0         |      |        | 98H 00H              | 99H 00H  | 9AH 00H  | 9BH 55H  |                       | 9DH 00H   | 9EH 00H   |                    |

|                    |      |    |              |      |    |               |       | T2EX       | T2            | BITS | \      | P1 <sup>1, 2</sup>   | I2CADD1  | I2CADD2  | I2CADD3  | NOT USED              | NOT USED  | NOT USED  | NOT USED           |

| 97H 1              | 96H  | 1  | 95H 1        | 94H  | 1  | 93H 1         | 92H   | 1 91H ′    | 90H 1         | DITO |        | 90H FFH              | 91H 7FH  | 92H 7FH  | 93H 7FH  |                       |           |           |                    |

| TF1                | TR   | R1 | TF0          | TR   | 20 | IE1           | IT1   | IE0        | IT0           | ріте | \      | TCON1                | TMOD     | TL0      | TL1      | TH0                   | TH1       | RESERVED  | RESERVED           |

| 8FH 0              | 8EH  | 0  | 8DH 0        | 8CH  | 0  | 8BH 0         | 8AH   | 89H (      | 88H 0         | BITS |        | 88H 00H              | 89H 00H  | 8AH 00H  | 8BH 00H  | 8CH 00H               | 8DH 00H   | LEGERTED  |                    |

|                    |      |    |              |      |    |               |       |            |               |      | \      | P0 <sup>1</sup>      | SP       | DPL      | DPH      | DPP                   |           |           | PCON               |

| 87H 1              | 86H  | 1  | 85H 1        | 84H  | 1  | 83H 1         | 82H   | 1 81H      | 80H 1         | BITS | 2      | 80H FFH              | 81H 07H  | 82H 00H  | 83H 00H  | 84H 00H               | RESERVED  | RESERVED  | 87H 00H            |

|                    |      |    |              |      |    |               |       |            |               |      |        |                      | 1 - /    |          | 1 - 311  |                       |           |           |                    |

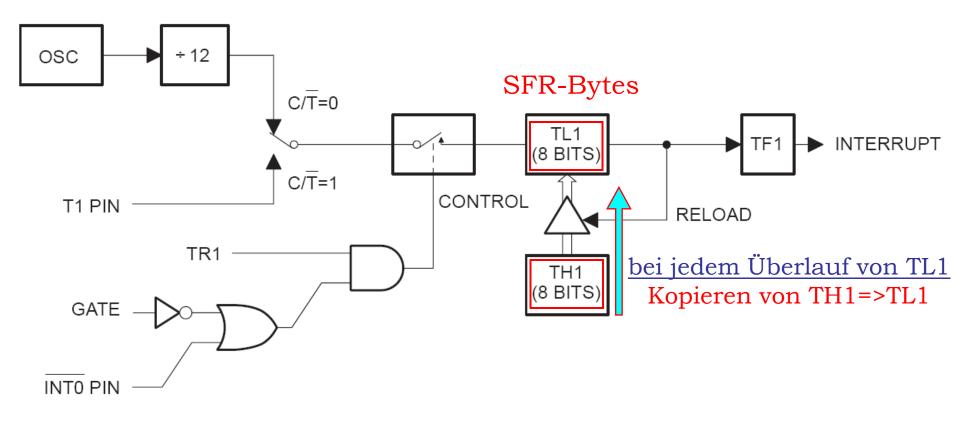

## Blockschaltbild zur Funktion von Timer "T1" in der Betriebsart 2

#### 'Autoreload'

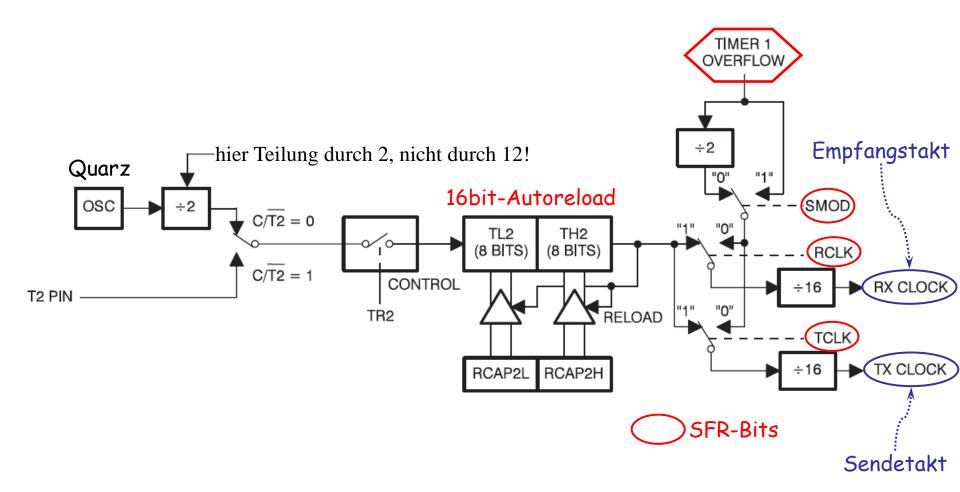

# Timer T2 als Baudratengenerator für die serielle Schnittsstelle ggf. zusammen mit Timer T1

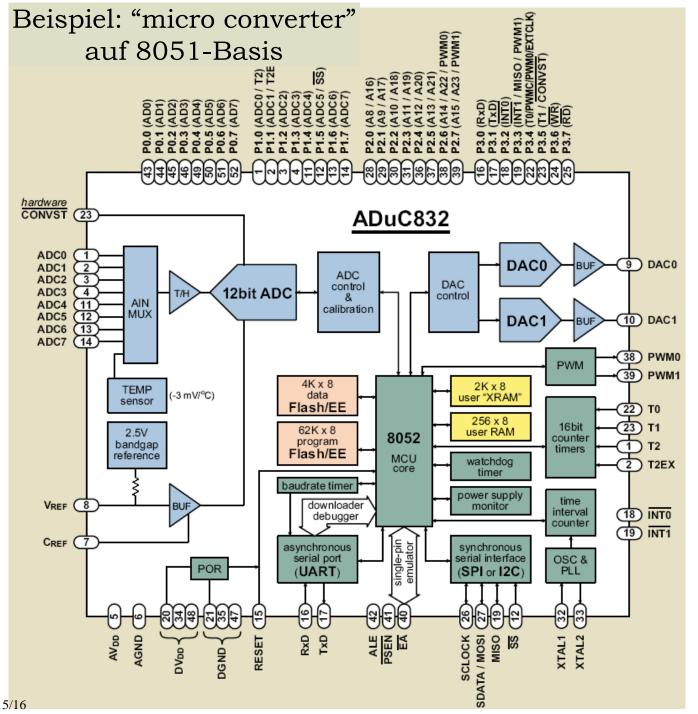

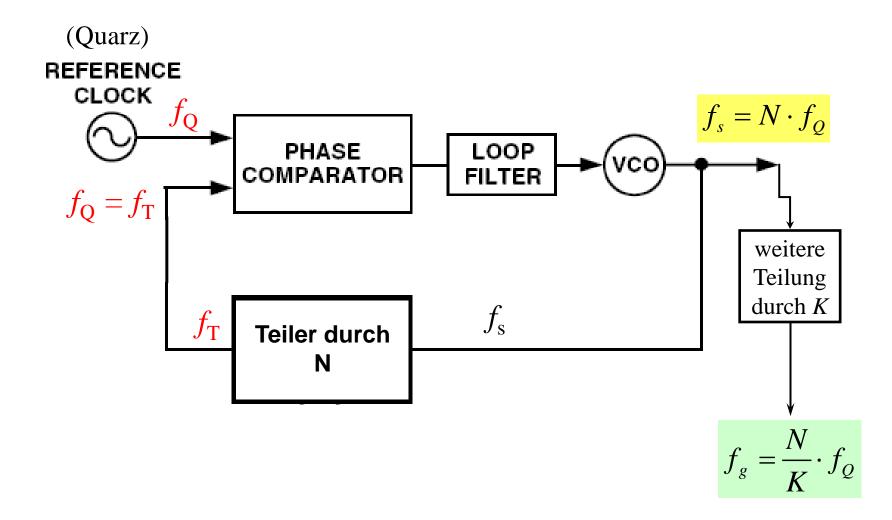

**Beispiel ADuC8xx**: Mittels PLL wird eine Uhrenquarzfrequenz von 2<sup>15</sup>Hz =32,768kHz mit dem Faktor 2<sup>9</sup>=512 multipliziert.

Dann ist die "Kerntaktfrequenz"  $f_c$ = 2<sup>24</sup>Hz ≈ 16,8MHz

$f_{\rm c}$  kann bei Bedarf durch programmierbare Binärteiler verkleinert werden

Baudrate:

$$b = \frac{f_c}{32 \cdot (2^{16} - RCAP2H, RCAP2L)}$$

| einige gebräuchliche mit Timer 2 erzeugbare Baudraten (ADuC832) |                   |               |               |                             |             |  |  |  |  |  |

|-----------------------------------------------------------------|-------------------|---------------|---------------|-----------------------------|-------------|--|--|--|--|--|

| Idealwert der<br>Baudrate                                       | Kerntakt<br>(MHz) | RCAP2H<br>HEX | RCAP2L<br>HEX | realer Wert der<br>Baudrate | Fehler in % |  |  |  |  |  |

| 19200                                                           | 16,777216         | FF            | E5            | 19418                       | +1,135      |  |  |  |  |  |

| 9600                                                            | 16,777216         | FF            | C9            | 9532,51                     | -0,703      |  |  |  |  |  |

| 4800                                                            | 16,777216         | FF            | 93            | 4809,98                     | +0,208      |  |  |  |  |  |

| 2400                                                            | 16,777216         | FF            | 26            | 2404,99                     | +0,208      |  |  |  |  |  |

| 1200                                                            | 16,777216         | FE            | 4B            | 1199,74                     | -0,0213     |  |  |  |  |  |

| 9600                                                            | 2,097152          | FF            | F9            | 9362,29                     | -2,476      |  |  |  |  |  |

| 4800                                                            | 2,097152          | FF            | F2            | 4681,14                     | -2,476      |  |  |  |  |  |

| 2400                                                            | 2,097152          | FF            | E5            | 2427,26                     | +1,135      |  |  |  |  |  |

| 1200                                                            | 2,097152          | FF            | C9            | 1191,56                     | -0,703      |  |  |  |  |  |

# Standard-PLL zur Frequenzsynthese (N, K ganzzahlig)

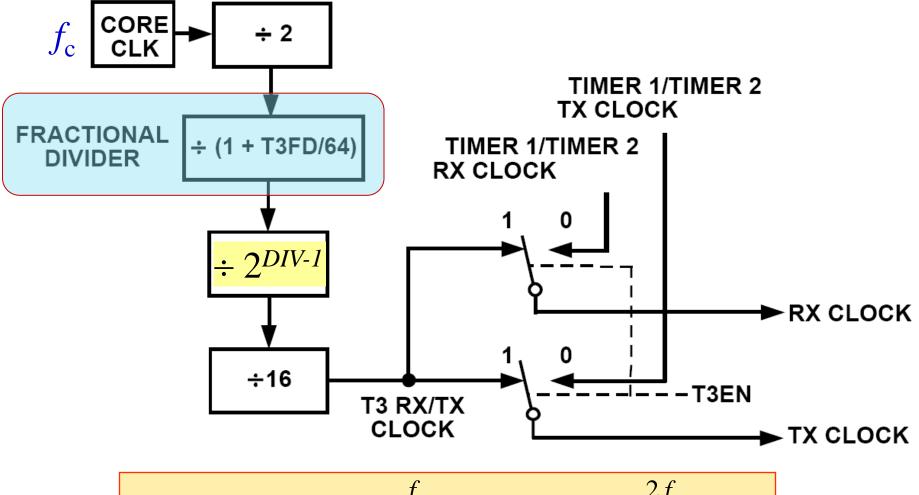

# Ein spezieller Timer mit 'Fraktionalteiler' zur flexibeln Baudratenerzeugung (T3 im ADuC832)

Baudrate:

$$b = \frac{f_c}{32 \cdot 2^{DIV-1} \left[1 + \frac{T3FD}{64}\right]} = \frac{2f_c}{2^{DIV-1} \cdot \left(T3FD + 64\right)}$$

| Bit        | Name               | Beschreibung                                                                                                                                                                                                                                  |      |      |            |  |  |  |  |  |

|------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------------|--|--|--|--|--|

| 7 T3BAUDEN |                    | T3 UART BAUD ENABLE Bit: Selektiert Timer 3 als Baudratengenerator. Wenn es gesetzt wird, werden die Bits PCON.7, T2CON.4 und T2CON.5 ignoriert. Wenn es "0" ist, erfolgt die Baudratengenerierung wie in einem Standard-8052-Mikrocontroller |      |      |            |  |  |  |  |  |

| 6          |                    | _                                                                                                                                                                                                                                             |      |      |            |  |  |  |  |  |

| 5          |                    | _                                                                                                                                                                                                                                             |      |      |            |  |  |  |  |  |

| 4          |                    |                                                                                                                                                                                                                                               |      |      |            |  |  |  |  |  |

| 3          |                    |                                                                                                                                                                                                                                               |      |      |            |  |  |  |  |  |

| 2          | DIV2               | binärer Teilfaktor                                                                                                                                                                                                                            |      |      |            |  |  |  |  |  |

| 1          | DIV1               | DIV2                                                                                                                                                                                                                                          | DIV1 | DIV0 | Teilfaktor |  |  |  |  |  |

| 0          | DIV0               | 0                                                                                                                                                                                                                                             | 0    | 0    | 1          |  |  |  |  |  |

|            |                    | 0                                                                                                                                                                                                                                             | 0    | 1    | 2          |  |  |  |  |  |

|            |                    | 0                                                                                                                                                                                                                                             | 1    | 0    | 4          |  |  |  |  |  |

| CIE        | das                | 0                                                                                                                                                                                                                                             | 1    | 1    | 8          |  |  |  |  |  |

|            | R T3CON<br>ADuC8xx | 1                                                                                                                                                                                                                                             | 0    | 0    | 16         |  |  |  |  |  |

|            | ADuCOAA            | 1                                                                                                                                                                                                                                             | 0    | 1    | 32         |  |  |  |  |  |

|            |                    | 1                                                                                                                                                                                                                                             | 1    | 0    | 64         |  |  |  |  |  |

|            |                    | 1                                                                                                                                                                                                                                             | 1    | 1    | 128        |  |  |  |  |  |

# Einige Möglichkeiten der Baudratenerzeugung mit Timer 3 (ADuC832)

| ideale<br>Baudrate | CD f <sub>c</sub> /MHz | DIV 2 <sup>DIV-1</sup> | T3CON | T3FD | reale<br>Baudrate | Fehler in % |

|--------------------|------------------------|------------------------|-------|------|-------------------|-------------|

| 230.400            | 0 16,77                | 2 2                    | 82H   | 09H  | 229.825           | -0,25       |

| 115200             | 0 16,77                | 3 4                    | 83H   | 09H  | 114.912           | -0,25       |

| 115200             | 1 8,388                | 2 2                    | 82H   | 09H  | 114.912           | -0,25       |

| 115200             | 2 4,194                | 1 1                    | 81H   | 09H  | 114.912           | -0,25       |

| 57600              | 0 16,77                | 4 8                    | 84H   | 09H  | 57.456            | -0,25       |

| 57600              | 1 8,388                | 3 4                    | 83H   | 09H  | 57.456            | -0,25       |

| 57600              | 2 4,194                | 2 2                    | 82H   | 09H  | 57.456            | -0,25       |

| 57600              | 3 2,097                | 1 1                    | 81H   | 09H  | 57.456            | -0,25       |

| 38400              | 0 16,77                | 4 8                    | 84H   | 2DH  | 38.480            | 0,208       |

| 38400              | 1 8,388                | 3 4                    | 83H   | 2DH  | 38.480            | 0,208       |

| 38400              | 2 4,194                | 2 2                    | 82H   | 2DH  | 38.480            | 0,208       |

| 38400              | 3 2,097                | 1 1                    | 81H   | 2DH  | 38.480            | 0,208       |

| 19200              | 0 16,77                | 5 16                   | 85H   | 2DH  | 19.240            | 0,208       |

| 19200              | 1 8,388                | 4 8                    | 84H   | 2DH  | 19.240            | 0,208       |

| 19200              | 2 4,194                | 3 4                    | 83H   | 2DH  | 19.240            | 0,208       |

| 19200              | 3 2,097                | 2 2                    | 82H   | 2DH  | 19.240            | 0,208       |

| 19200              | 4 1,048                | 1 1                    | 81H   | 2DH  | 19.240            | 0,208       |

| 9600               | 0 16,77                | 6 32                   | 86H   | 2DH  | 9.620             | 0,208       |

| 9600               | 1 8,388                | 5 16                   | 85H   | 2DH  | 9.620             | 0,208       |

| 9600               | 2 4,194                | 4 8                    | 84H   | 2DH  | 9.620             | 0,208       |

| 9600               | 3 2,097                | 3 4                    | 83H   | 2DH  | 9.620             | 0,208       |

| 9600               | 4 1,048                | 2 2                    | 82H   | 2DH  | 9.620             | 0,208       |

| 9600               | 5 0,524                | 1 1                    | 81H   | 2DH  | 9.620             | 0,208       |

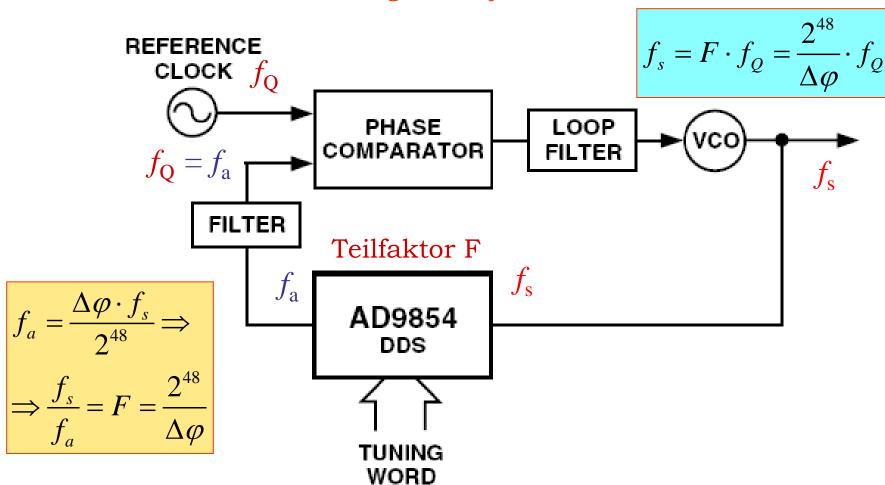

# Grundlagen der 'fraktionalen' Frequenzsynthese mit feinstufigem Faktor *F*: PLL kombiniert mit DDS

- Direkter Digitaler Synthesizer - => Kap. 4.2, S. 111

$\Delta \phi \in \{1....2^{48}\} \Rightarrow 281.474.976.710.656$  Schritte sind möglich

Billionen

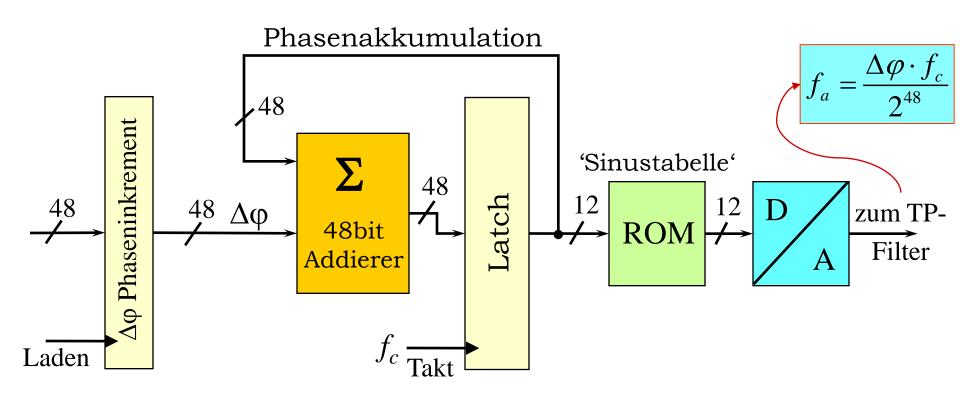

## Grundaufbau eines direkten digitalen Synthesizers (DDS)

detaillierte Analyse folgt im Kapitel 4: "Digitale Frequenzsynthese"

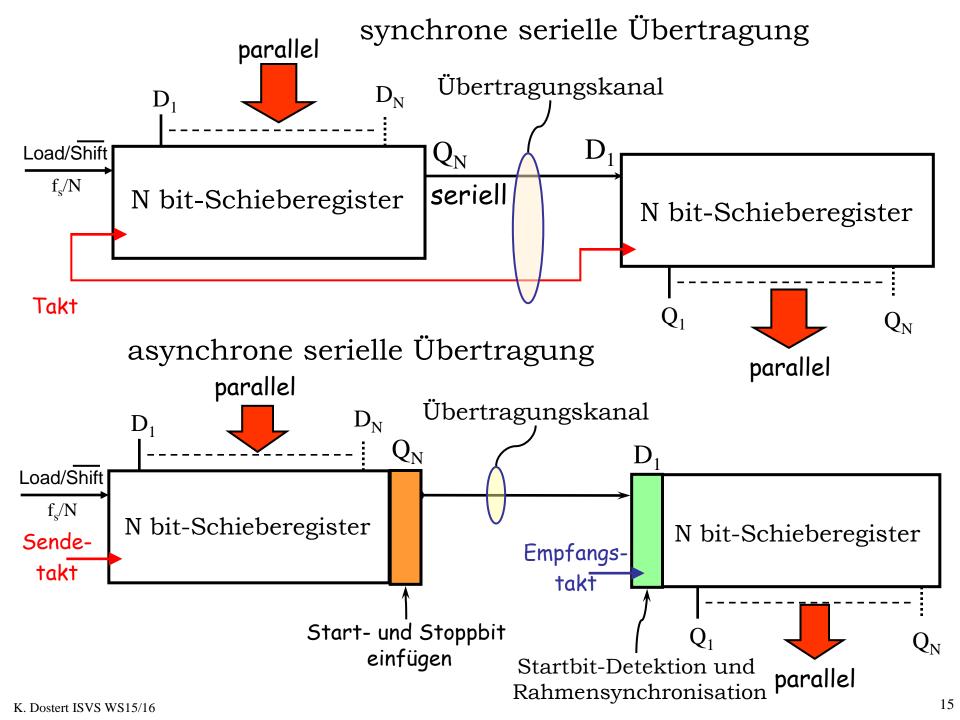

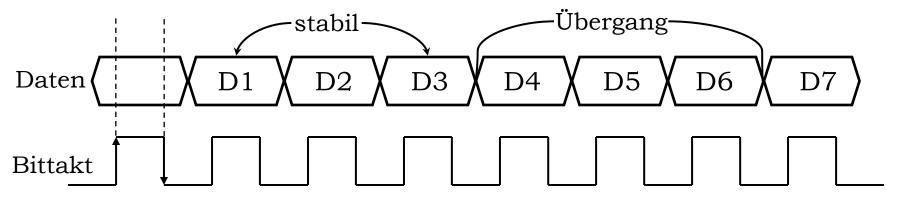

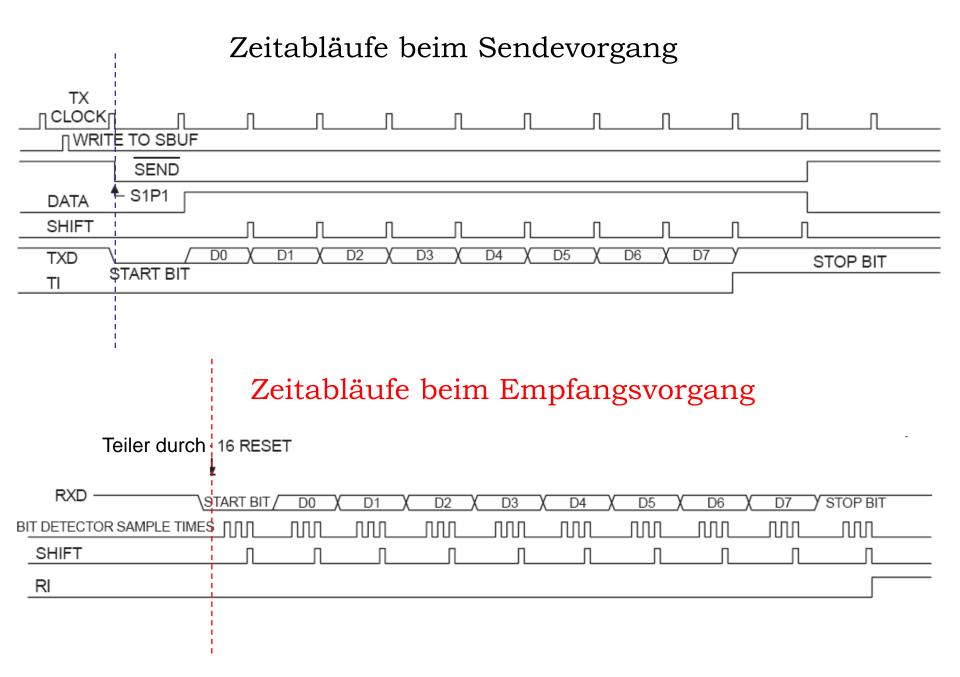

Signalverlauf und Taktung bei synchroner serieller Übertragung

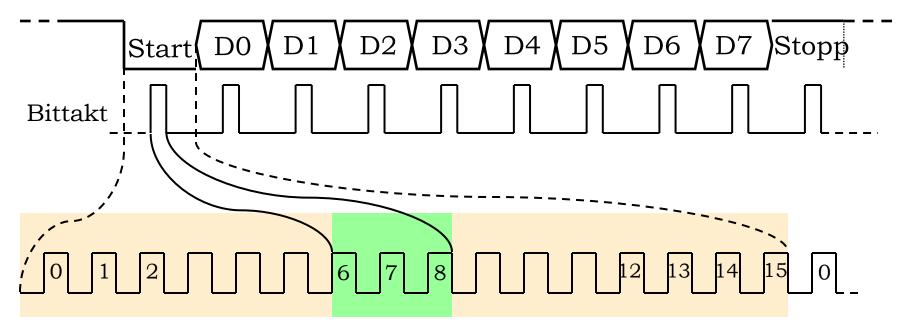

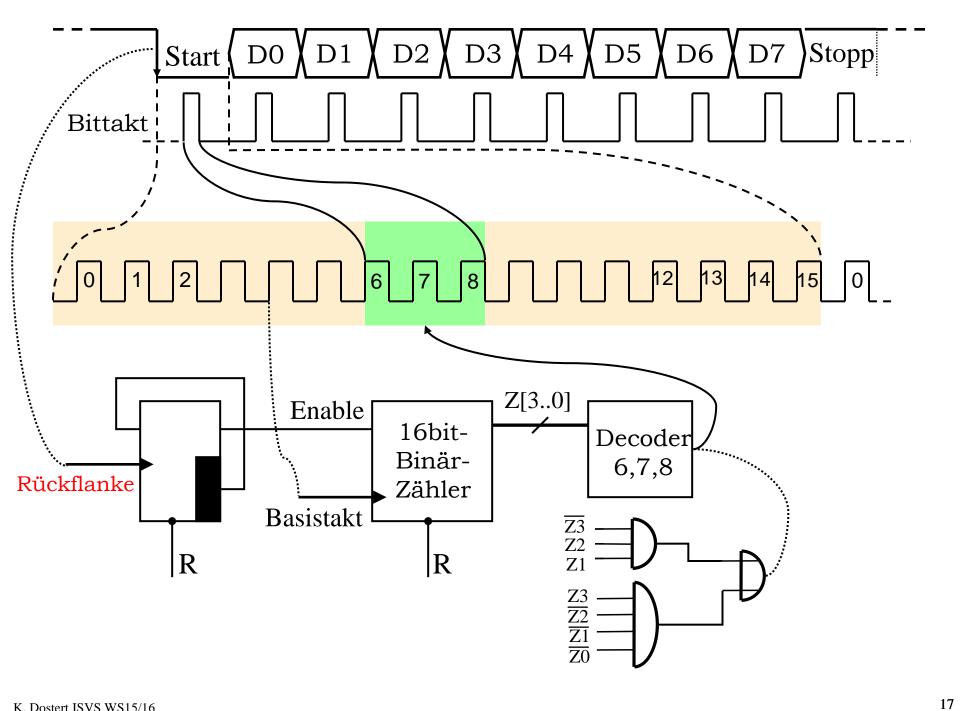

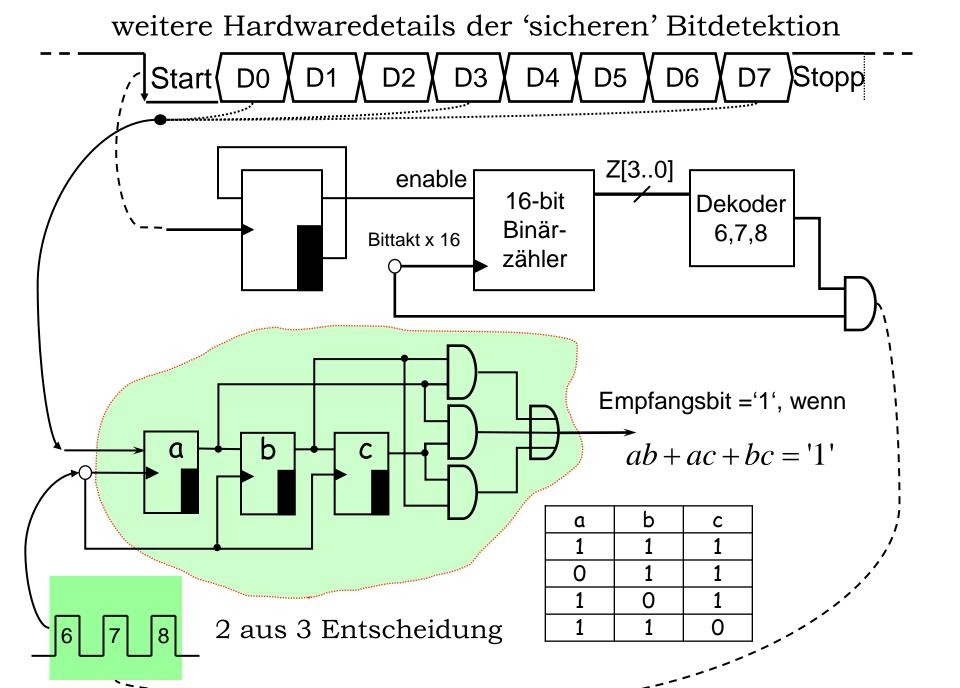

Start/Stopp-Verfahren zur asynchronen seriellen Übertragung

Basistakt: 16-facher Bittakt

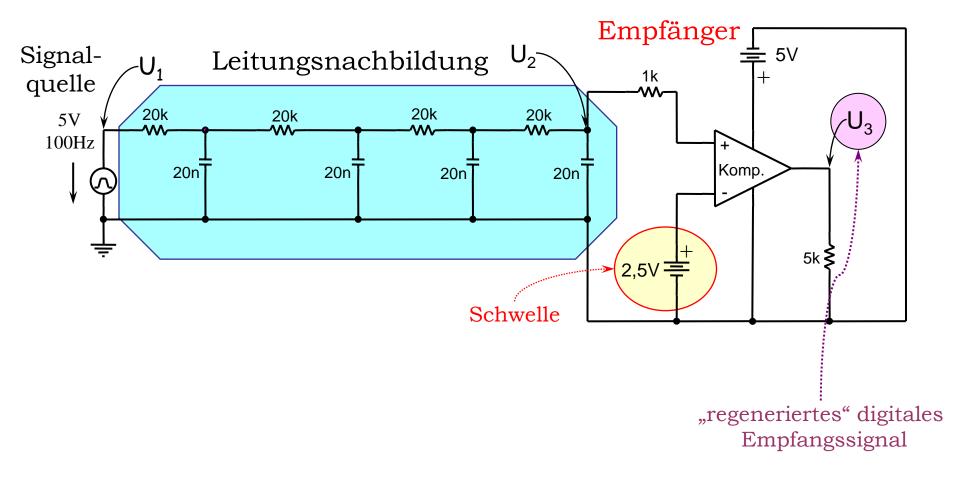

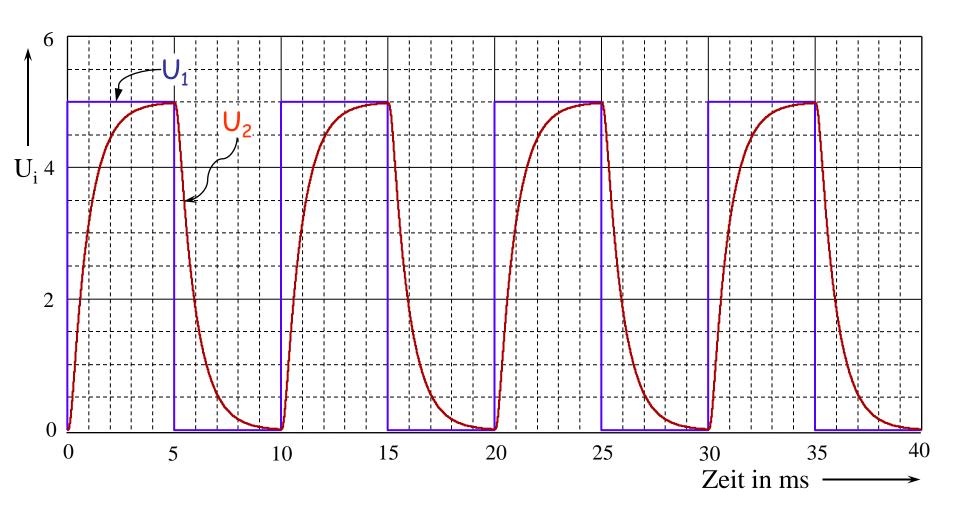

# Analyse einer seriellen Datenübertragung über eine Leitung

# RC-Kette: 10k, 10nF

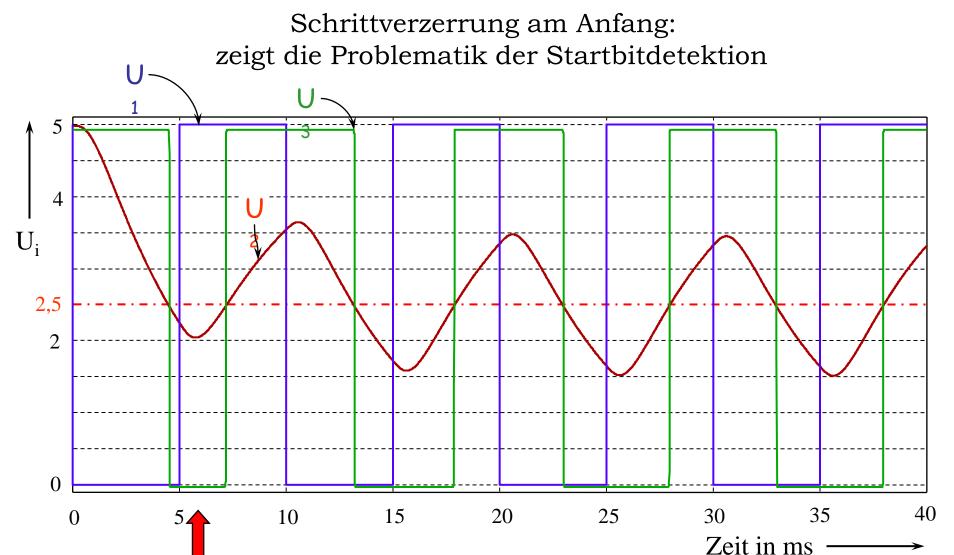

RC-Kette: 20k, 30nF, Detektion mit optimaler Schwelle von 2,5V

deutlich verkürztes Startbit

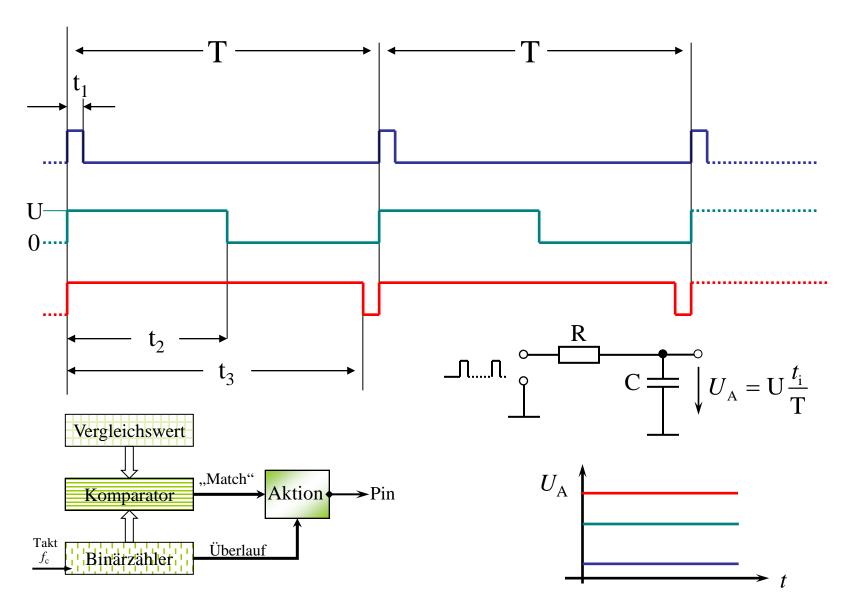

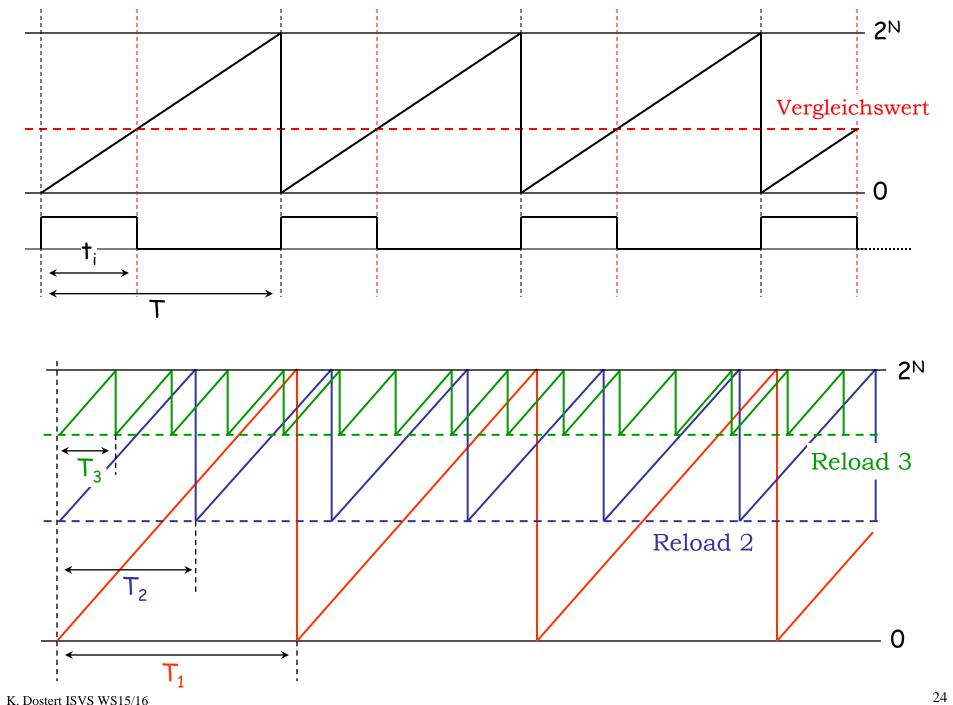

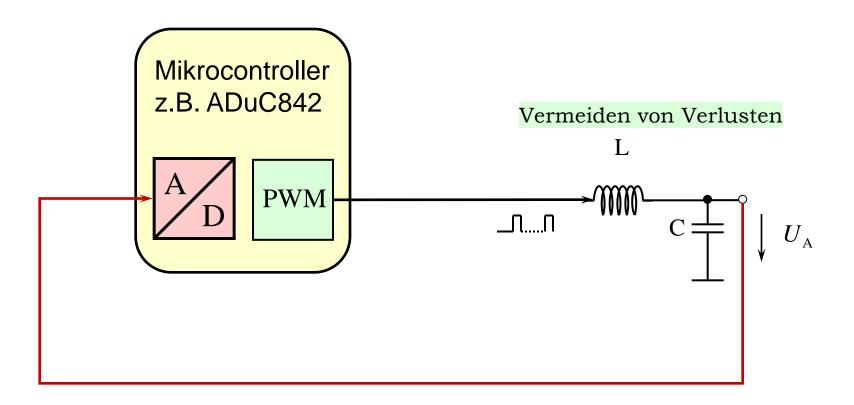

# D/A-Wandlung mittels Pulsweitenmodulation

# Prinzip eines analogen Schaltnetzteils mit PWM

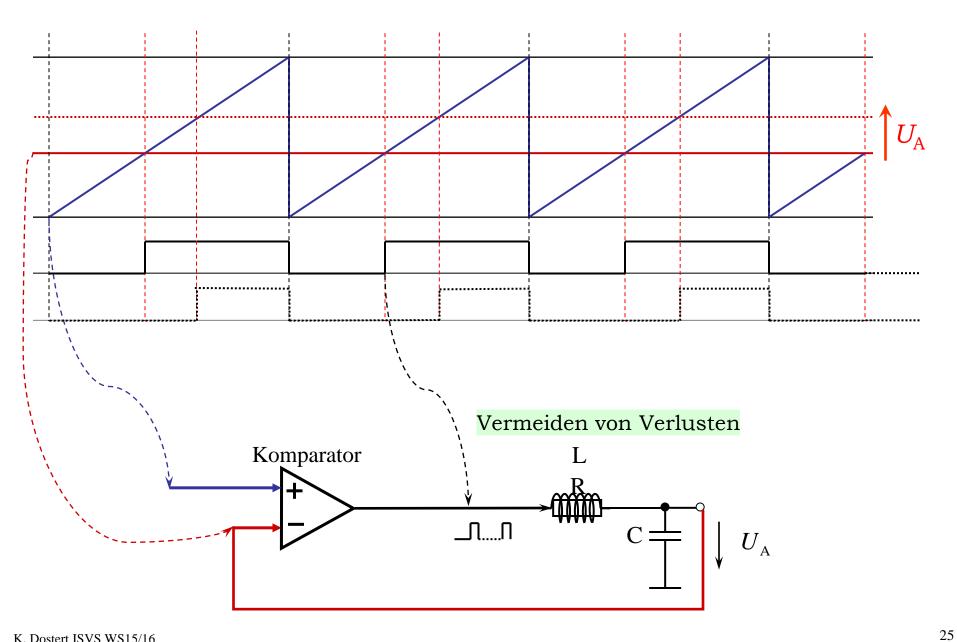

K. Dostert ISVS WS15/16  $\Rightarrow$ LT\_3972  $\Rightarrow$ LT\_3972\_v

26

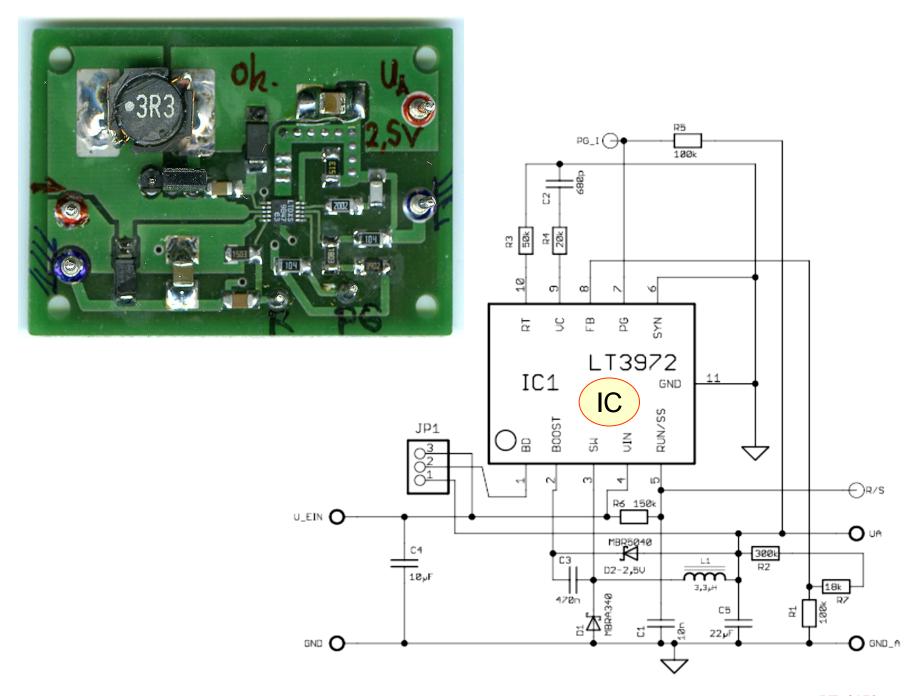

# Prinzip des digitalen Schaltnetzteils mit PWM

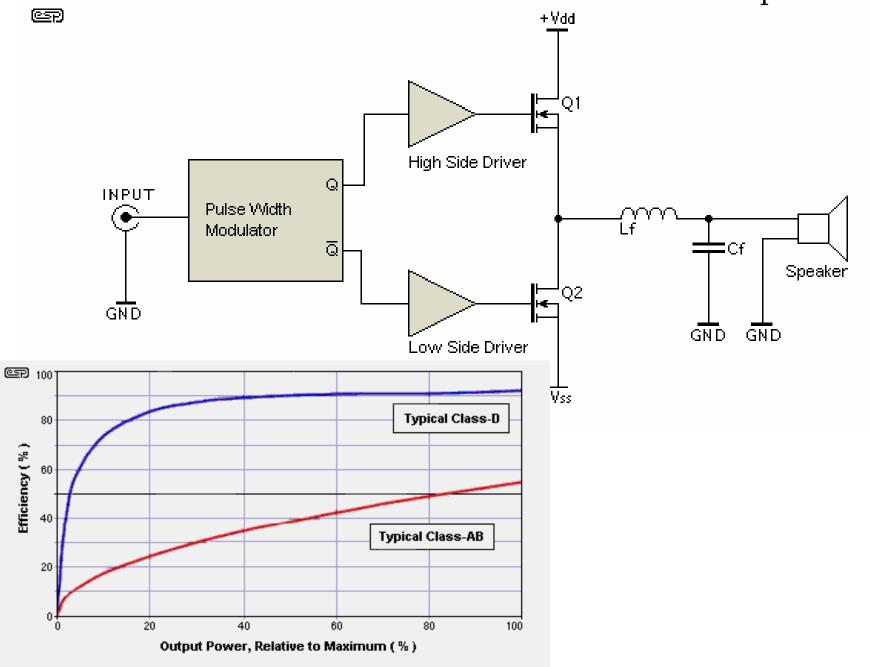

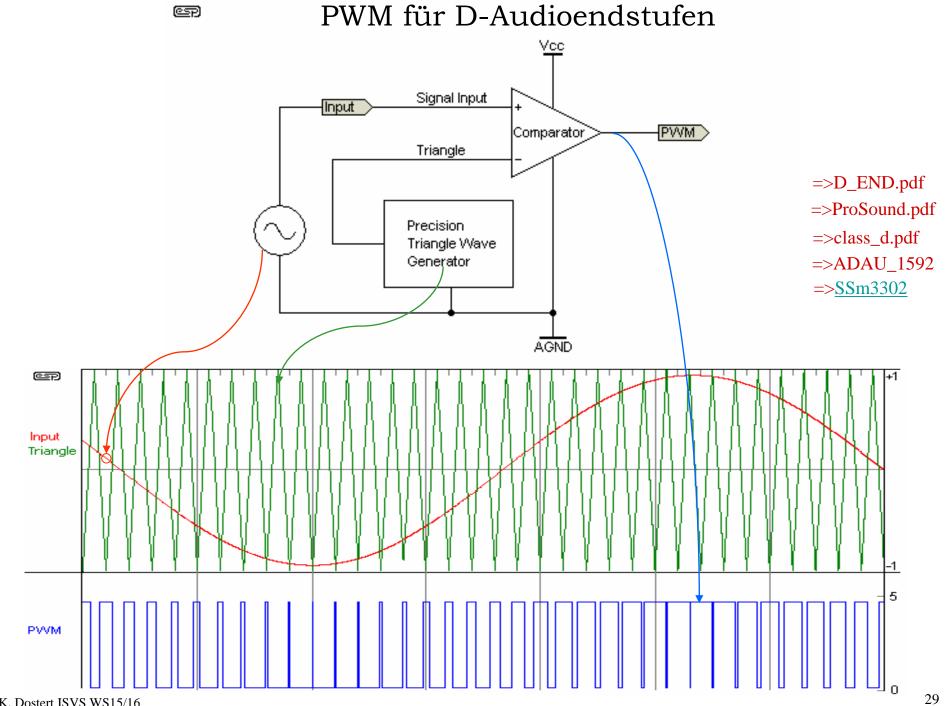

## D-Audioendstufen nach dem PWM-Prinzip

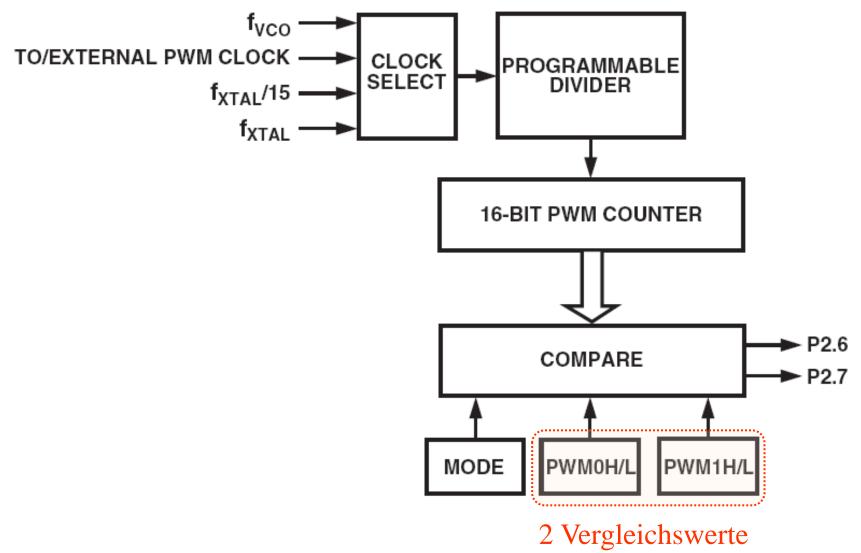

# Erweiterte PWM-Strukturen in Mikroconvertern vom Typ ADuC8xx

30

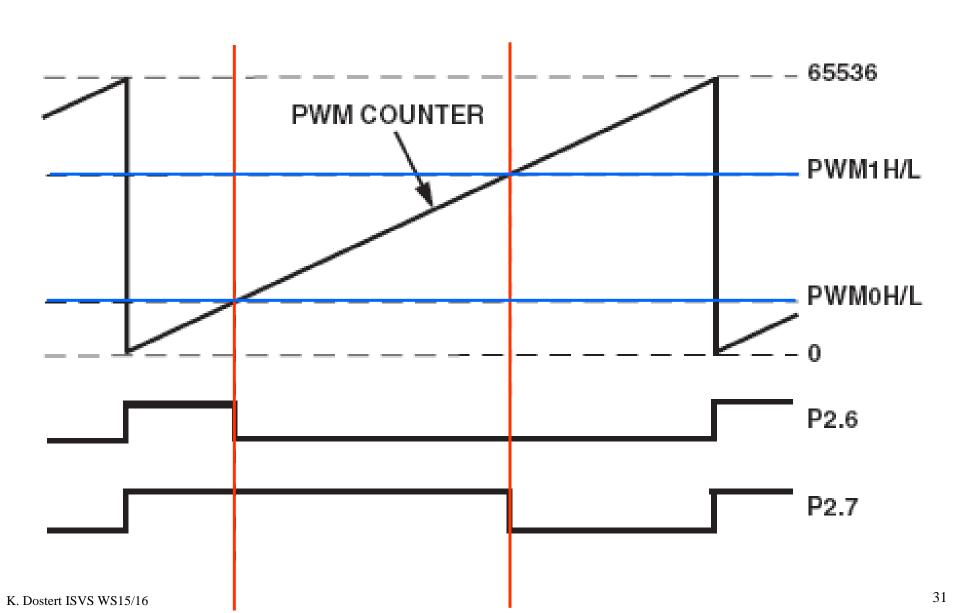

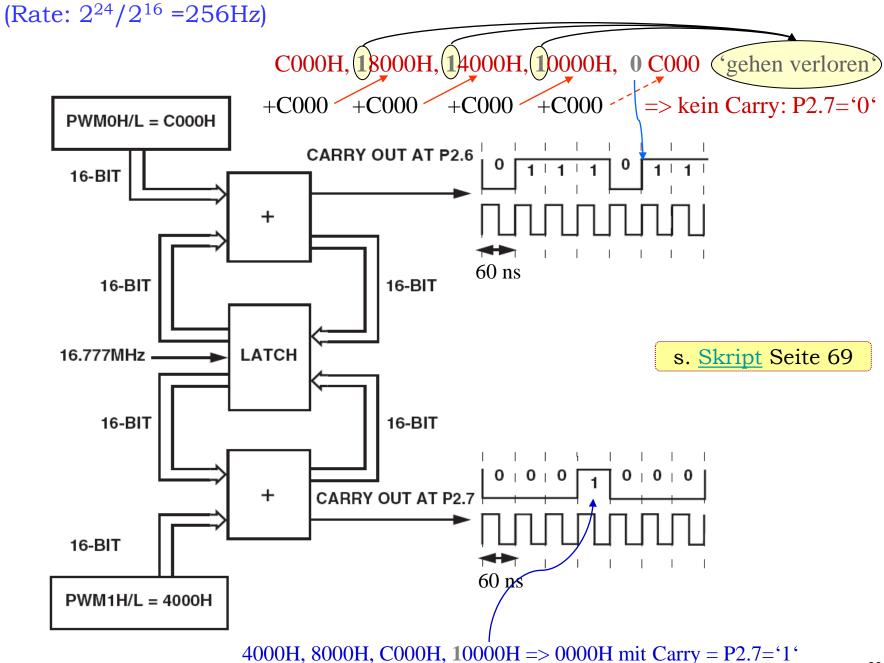

# Zweifach-PWM mit 16 bit Auflösung

- die beiden PWM-Ausgänge sind synchronisiert -

PWM mit 'Sigma-Delta-Prinzip' lange Periodendauer 1/256Hz ≈3,9ms

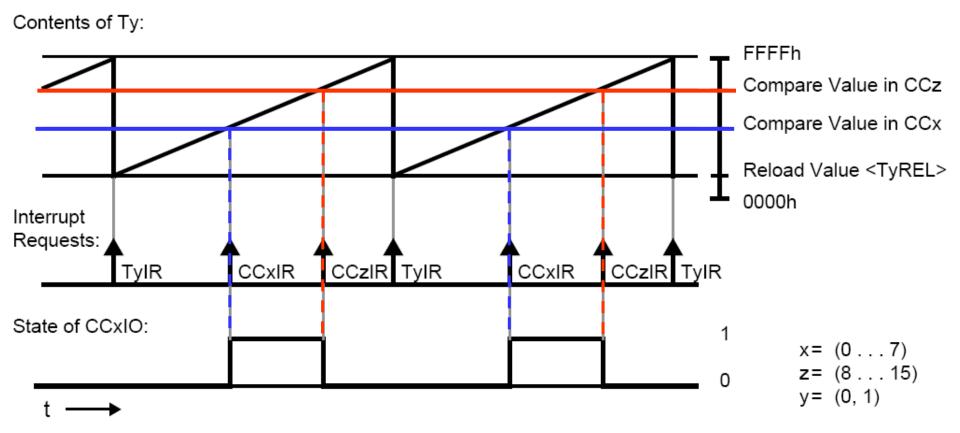

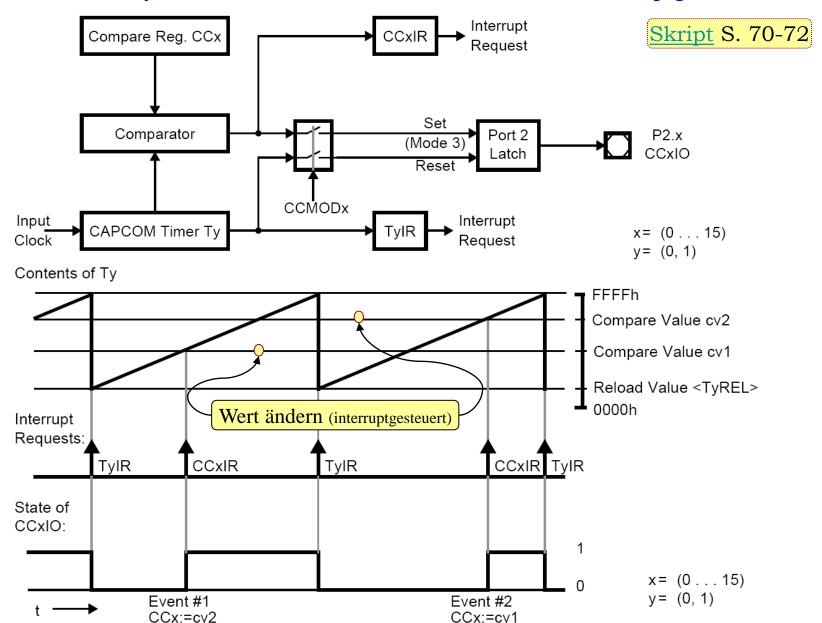

#### Merkmale der PWM-Struktur im 80C166:

MODE 3 mit dynamisch veränderbarem Tastverhältnis (interruptgesteuert)

33

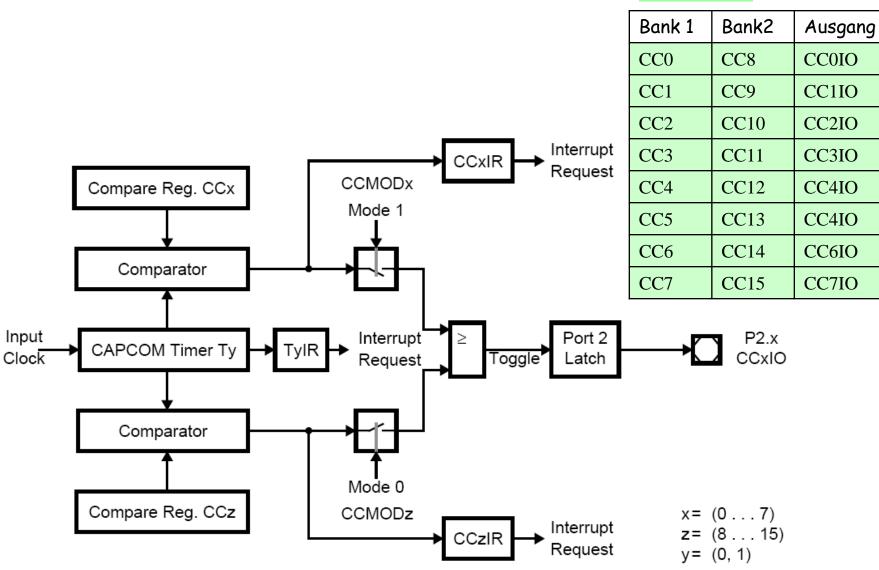

## Zum Double-Register-Compare-Modus

#### CCx CCz

Pin

P2.0

P2.1

P2.2

P2.3

P2.4

P2.5

P2.6

P2.7

Im Double-Register-Compare-Mode können, losgelöst von Timerüberläufen, bis zu 8 Impulsfolgen an den Pins 2.0...2.7 mit unterschiedlichem aber festem Tastverhältnis programmiert werden, die ohne Softwareeingriffe ablaufen.

- interruptgesteuert können die Tastverhältnisse dynamisch verändert werden -